Static Noise Margin: Understanding Digital Circuit Reliability

Static Noise Margin: Understanding Digital Circuit Reliability

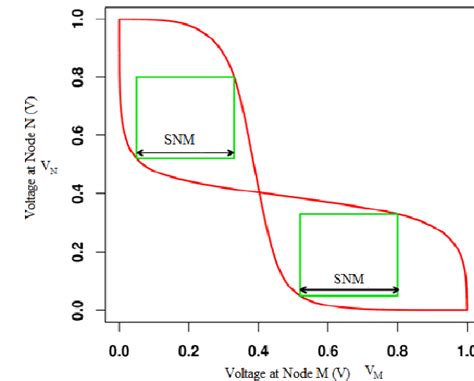

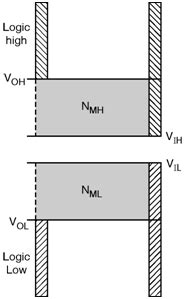

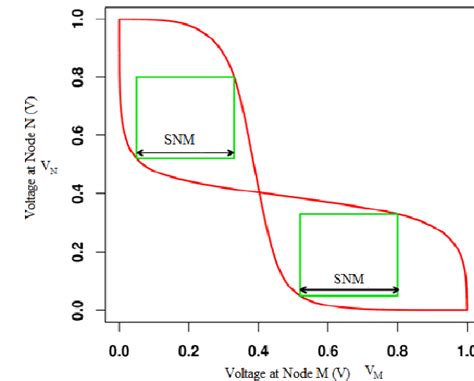

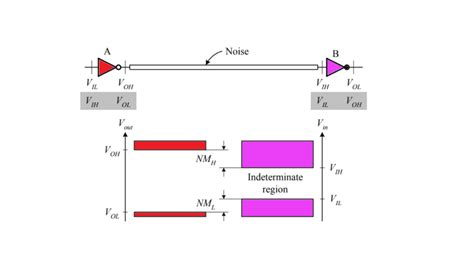

In digital electronics, the reliability of a circuit is crucial to its overall performance. One key factor that affects reliability is the static noise margin (SNM), which is a measure of a digital circuit’s ability to withstand noise and maintain its logical state. In this article, we will delve into the concept of SNM, its importance, and how it affects digital circuit reliability.

What is Static Noise Margin (SNM)?

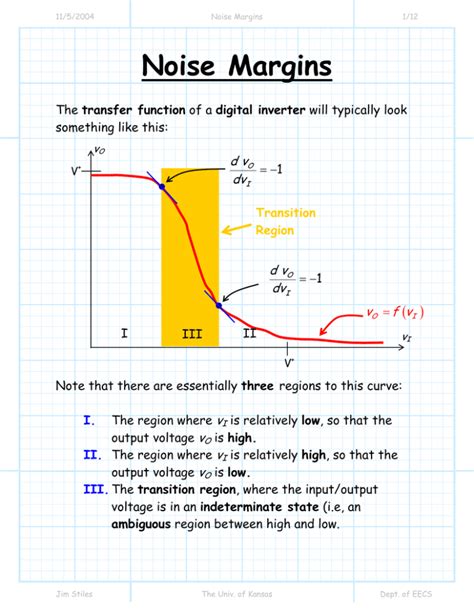

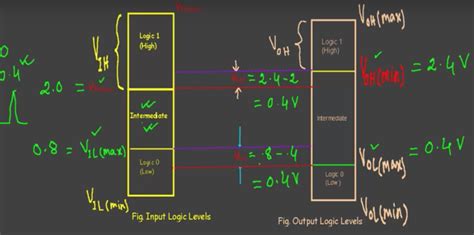

Static noise margin is a measure of the amount of noise that a digital circuit can tolerate without changing its logical state. It is defined as the difference between the signal voltage and the noise voltage that can be applied to a circuit without causing it to malfunction. In other words, SNM is a measure of how much noise a circuit can withstand before it becomes unreliable.

Importance of SNM in Digital Circuits

SNM is a critical parameter in digital circuit design because it directly affects the reliability of the circuit. A higher SNM indicates that a circuit is more resistant to noise and can maintain its logical state even in the presence of significant noise. This is particularly important in high-speed digital circuits, where noise can be generated by a variety of sources, including power supply noise, electromagnetic interference (EMI), and crosstalk.

A low SNM can lead to a range of problems, including:

- Bit flipping: When a circuit is unable to maintain its logical state due to noise, it can result in bit flipping, where a logic 0 is interpreted as a logic 1, or vice versa.

- Glitches: Noise can cause temporary changes in the logical state of a circuit, resulting in glitches that can propagate through the circuit and cause errors.

- Functional failures: In severe cases, a low SNM can lead to functional failures, where the circuit is unable to perform its intended function due to excessive noise.

Factors Affecting SNM

Several factors can affect the SNM of a digital circuit, including:

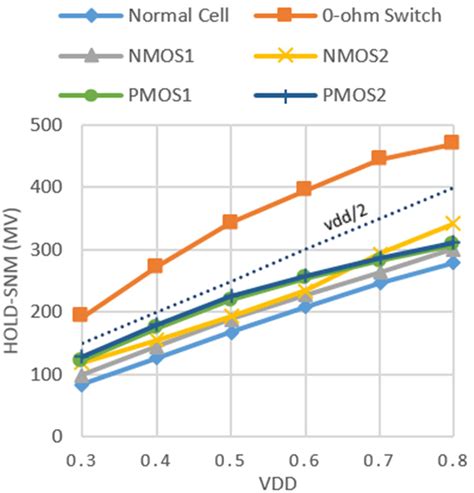

- Supply voltage: A lower supply voltage can reduce the SNM of a circuit, making it more susceptible to noise.

- Threshold voltage: The threshold voltage of a transistor can affect the SNM of a circuit, as it determines the voltage level at which the transistor switches between its on and off states.

- Noise sources: The presence of noise sources, such as power supply noise, EMI, and crosstalk, can reduce the SNM of a circuit.

- Circuit design: The design of the circuit itself can affect the SNM, including the choice of logic gates, the use of buffers, and the routing of signals.

Improving SNM in Digital Circuits

There are several techniques that can be used to improve the SNM of a digital circuit, including:

- Increasing supply voltage: Increasing the supply voltage can improve the SNM of a circuit, but this may also increase power consumption.

- Using noise-tolerant logic gates: Using logic gates that are designed to be noise-tolerant can improve the SNM of a circuit.

- Adding buffers: Adding buffers to a circuit can help to isolate noise sources and improve the SNM.

- Optimizing circuit design: Optimizing the design of a circuit, including the choice of logic gates and the routing of signals, can help to improve the SNM.

Conclusion

Static noise margin is a critical parameter in digital circuit design, as it directly affects the reliability of the circuit. By understanding the factors that affect SNM and using techniques to improve it, designers can create digital circuits that are more resistant to noise and more reliable in their operation.

What is the difference between static noise margin and dynamic noise margin?

+

Static noise margin refers to the ability of a digital circuit to withstand noise when it is in a static state, whereas dynamic noise margin refers to the ability of a digital circuit to withstand noise when it is switching between states.

How can I improve the static noise margin of a digital circuit?

+

There are several techniques that can be used to improve the static noise margin of a digital circuit, including increasing the supply voltage, using noise-tolerant logic gates, adding buffers, and optimizing circuit design.

What are the consequences of a low static noise margin in a digital circuit?

+

A low static noise margin can lead to a range of problems, including bit flipping, glitches, and functional failures.